1.基础知识

硅(Si)是一种半导体,通常作为数字芯片的物理材料。由于它的所有价电子都参与了化学键,因此纯净硅是一种不良导体。但是它的导电性可以在硅中引入称为参杂剂的少量杂质来提高。在硅中加入V族元素的杂质砷,这时候会多出一些电子,这些电子可以携带电流,在电压的作用下流动起来,提高了导电性,这类半导体称之为n型半导体。类似地,在硅中加入III族元素的杂质硼,会多出一些具有带正电荷属性的“空穴”,这类半导体称为p型半导体。

P型与n型硅组合在一起,变成一个PN结(二极管)。P型半导体称为阳极(anode),n型半导体称为阴极(cathode)。给p端给高压,n端给低压,即p端电压高于n端电压时,二极管导通,就会有电流流过,否则,二极管不导通。

通过PN结,可以实现信号的传递,但是,只有一个PN结,我们无法控制信号的准确传递,比如数字信号大多数情况下,当某个信号为1时,我们需要信号从A端传递到B端,显然,一个PN结无法做到,因此,将PN结进行不同组合,再加入一个控制端,就构成了nMOS管和pMOS管。

nMOS管如下图所示,每个晶体管由一层栅(Gate)、一层SiO2绝缘层以及一层硅基底堆叠构成,硅基底也称为衬底(substrate)、体(body)或体硅(bulk)。在p型衬底上有两个与栅(Gate)相邻的区域,分别为源(Source)和漏(Drain)。衬底通常接地。栅极作为控制端,影响电流在源和漏之间的流动,在Gate端给高电压(逻辑值为1),Source/Drain端给低电压(相对Gate端)时,源和漏之间导通,有电流流过,当Gate端为低电平时,nMOS管关断。pMOS的情形与nMOS管恰好相反。

在Gate与Body之间的SiO2绝缘层理想状态是不导电的,但是实际上因为寄生效应会出现漏电,而且随着芯片纳米工艺的进步,SiO2绝缘层可能会变薄,导致漏电情况可能会加重。

可以将MOS晶体管看作是一个开关模型,对nMOS管来说,Gate为低电平时,关断,为高电平时,导通。对pMOS管来说,Gate为低电平时,导通,为高电平时,关断。

2 CMOS逻辑

2.1 反相器

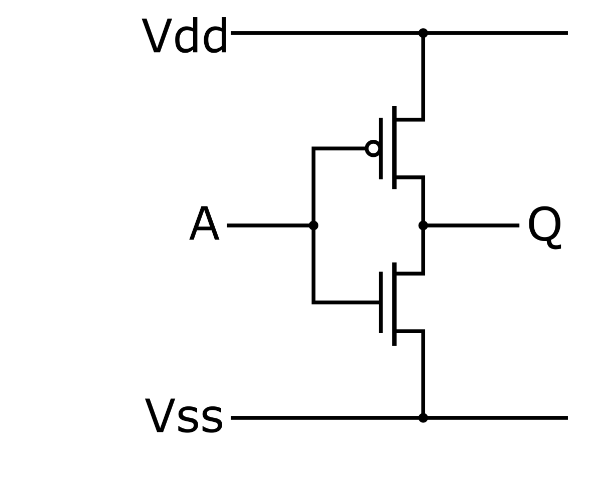

反相器即非(NOT)门,由1个nMOS管和1个pMOS管构成,当输入A为0时,nMOS管关断而pMOS管导通,输出Y被上拉至VDD,即输出1。相反,当输入A为1时,nMOS管导通而pMOS管关断,输出Y被下拉至GND,即输出0。

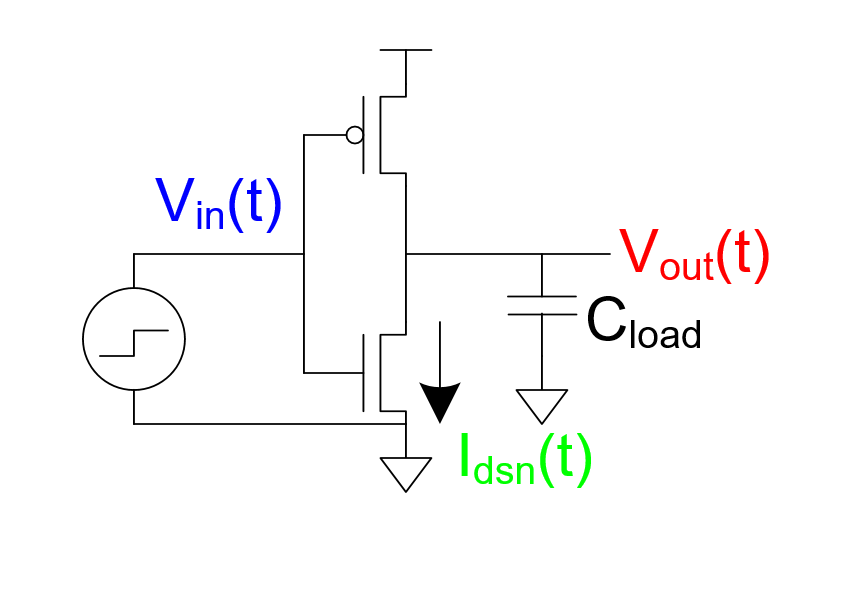

按照上述描述,理想状态为A电平改变,输出Y会立即改变,也就是这个反相器延迟为0,并且电平的改变(从1到0或从0到1)沿是竖直的,这样这个器件频率会很高。但是实际情况下,电路中Y端存在电容,并且导通后也存在电阻,也就是一个RC电路模型,因此,整个器件存在一定的延迟(Delay)。

反相器的RC电路模型如下图所示,可以看成是一个由Gate端控制的,对输出端电容充放电的过程。Gate为0时,pMOS管导通,对输出的电容进行充电,输出Y端电压升高至1;当Gate为1时,nMOS管导通,对输出的电容进行放电,输出Y端电压降低至0。充放电的整个过程并不是瞬间的,而是有时间的。

为了想整个电路跑的越快越好,第一,电容要小,电容小的话存的电荷就少,充放电过程就越快;第二,导通时的电流要大,电流大,对电容的充放电过程也越快。但是电流也与MOS管的工艺尺寸等都有关系,并不能无限制增大,而且,电流大,功耗也会大,因此,工艺厂商也会做一个平衡。

下图为反相器的输入电压与时间波形和输出电压与时间波形图,可以看到,电压从0变为1或者从1变为0都是有一个过程,并不是瞬间变化,所以,整个电路会有Delay产生。数字电路中“0”和“1”的定义如下:

-

高于VDD的80%,定义为数字电路中的“1”; -

低于VDD的20%,定义为数字电路中的“0”。

电路Transition(信号爬升时间)定义为同一个信号电平从0变为1或从1变为0的时间。也就是这个信号在两个电平之间的转换时间。分为Fall time和Rise time,Fall time即为VDD的80%(电平为1)到VDD的20%(电平为0)的时间,图中为tf;Rise time 为VDD的20%(电平为0)到VDD的80%(电平为1)的时间,图中为tr。器件的Transition参数都会在Cell library库里提供。

电路Delay(信号传输延时)定义为一个Cell的输入变化(50% VDD)到输出信号变化(50% VDD)的时间。包括上升沿传输延时(tpdr)和下降沿传输延时(tpdf)。

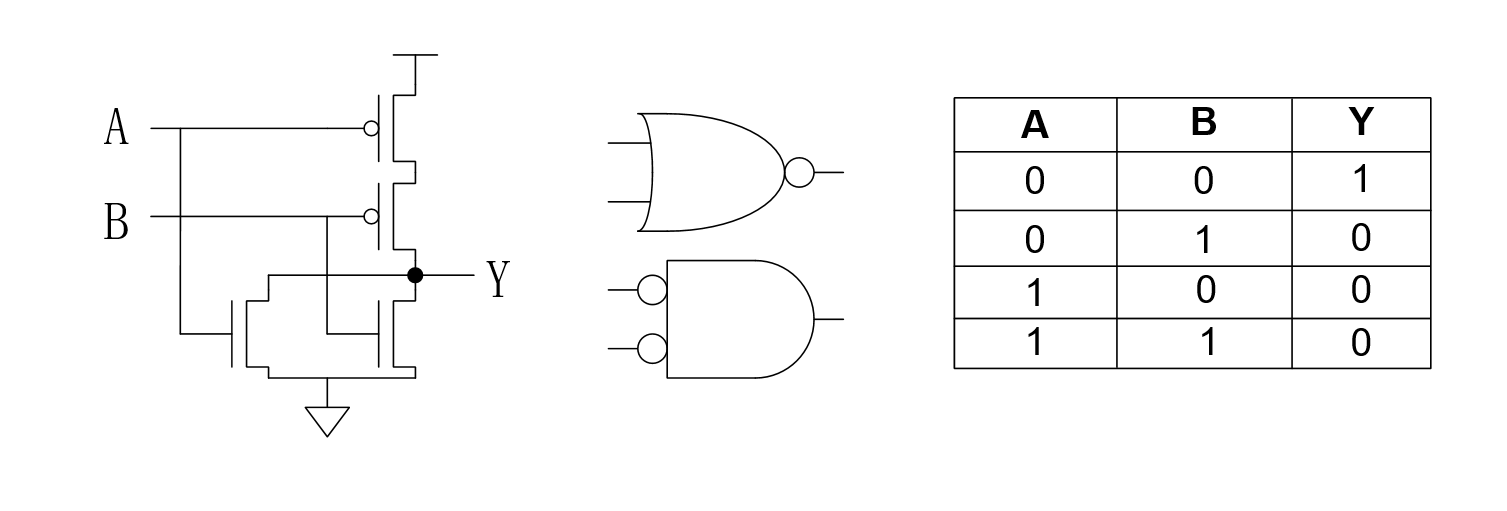

2.2 与非(NAND)门

下图为一个2输入的与非门,由两个在Y和VDD之间并联的pMOS管和两个Y和GND之间串联在一起的nMOS管构成。逻辑真值表如下图中表格所示。与非门当输入都为高时,输出为低;输入有低时,输出为高。即当输入有1个低电平时,Y连接至VDD,因此,可以推断出pMOS并联,可以用这种方式通过真值表画出电路图。

2.3 或非(NOR)门

下图为一个2输入的或非门,由两个在Y和VDD之间串联的pMOS管和两个Y和GND之间并联的nMOS管构成。逻辑真值表如下图中表格所示。

2.4 传输门

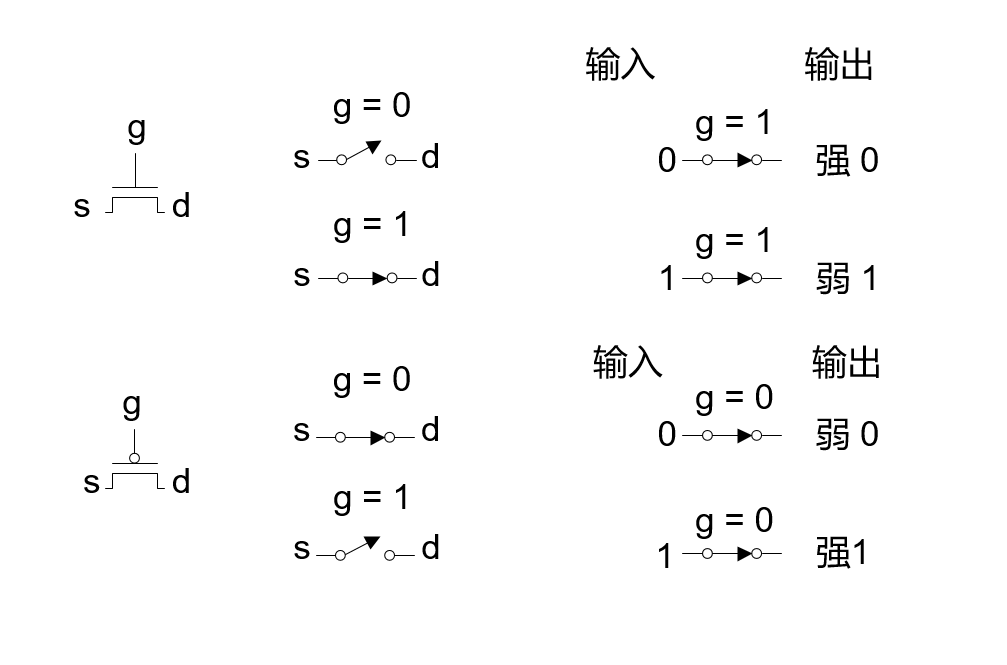

依据MOS管模电中的特性,nMOS管传输“强0弱1”,即nMOS从输入传输低电平0到输出,输出为强0,而传输高电平1时,输出的高电平会比输入的电压小,比如输入电压是VDD,那输出电压要小于VDD(但也是高电平)。pMOS管传输“强1弱0”。

如下图所示,s和d端其中一端都没有接VDD或GND,而是直接接输入、输出信号,那么在g=0时,关断,g=1时,s与d之间导通,但是出现输入到输出端的压降。

因此,设计出了传输门,由1个nMOS管和1个pMOS管并联在一起。对于功能来说,与单个MOS管相同,区别在于从输入传输至输出时,不会产生压降,如下图所示,g=1,gb=0时,不管输入为0还是为1,输出都是强的0或1。

传输门还可以用来做开关,还可以用来做触发器。

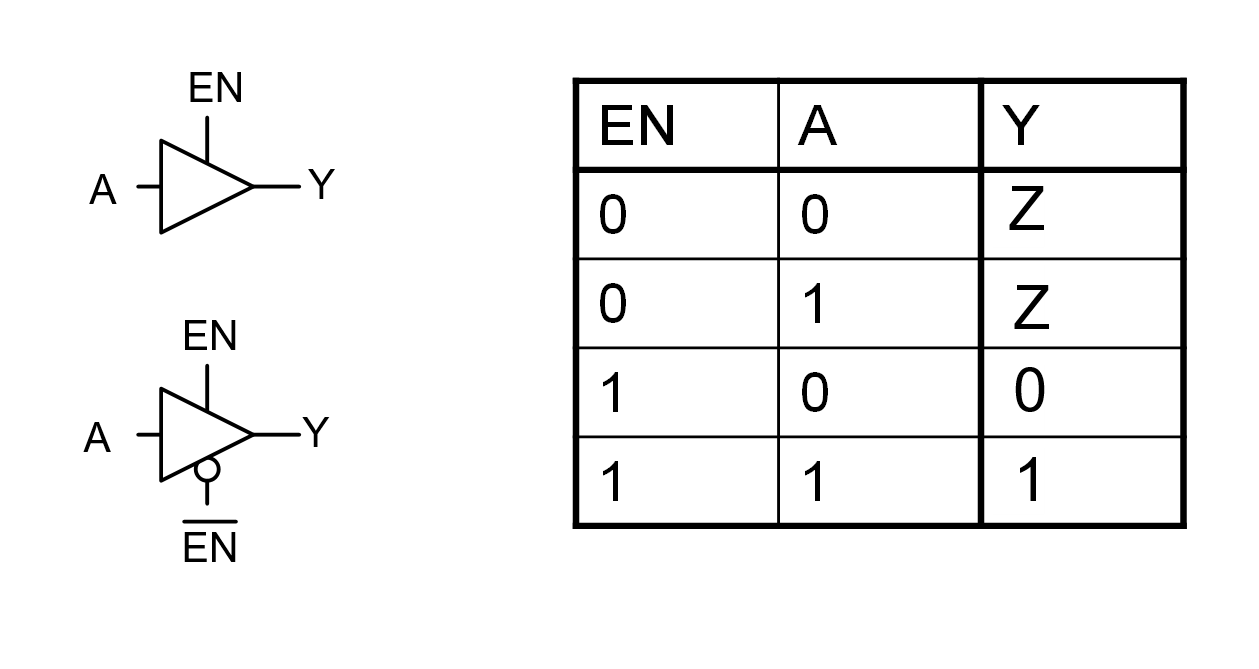

2.5 三态门(Tristate buffer)

三态门(三态缓冲器)如下图所示,当EN为1时,输出Y等于输入A,而当EN为0时,输出Y变为高阻态。通常会将EN和EN非都画出来,也可只画一个EN。高阻在物理上并不是没有电压,而是电压处于不确定状态,受自身或旁边Cell的影响。三态用的地方主要是一些协议的接口(比如I2C),作为输入输出。

为什么三态门一般只能做在芯片的IO上,不能做在芯片内部?

如下图所示,在三态门为高阻态的情况下,若输出端口受到附近cell的影响使得输出端口Y的电压在0.5VDD附近,会使得其后连接的反相器中的nMOS管和pMOS管均处于导通状态,相当于VDD直接接VSS,会导致静态功耗急剧增大,严重时会烧毁电路。而三态门处于IO上时,一般外部电路会有上下拉电阻,三态门的输出会被上拉到VDD或者下拉到GND。

3 电路延时影响因素

厂商出厂Cell以后,这个Cell电路的输入信号Transition和电容等都已经确定好了,这时候,影响电路延时的因素(PVT)主要如下:

-

Process:代工厂制造参数的漂移; -

Voltage:电压越高,电路延时越低; -

Temperature:PN结温度越高,电路延时越大。

参考资料

[1]:CMOS VLSI Design: https://book.douban.com/subject/4322694/

[2]:https://www.zhihu.com/question

/284058267

[3]:https://blog.csdn.net/weixin_39640090/article/details/112773282