DC综合实践

首先为工程设计建立好文件夹,如下图,设计目录为DC_proj1,设计目录中包含doc、rtl、syn等目录,doc目录用于存放工程文档,rtl目录用于存放设计rtl文件,syn用于DC综合。

syn目录下各子目录如上,其中work目录用于DC运行目录。在work目录下建立library目录用于存放TSMC 90nm工艺库。上述library目录下文件都为TSMC 90nm工艺库文件。

由于本次只是进行一个加法器综合,加法器RTL代码如下,所以work目录下不建立启动文件.synopsys_dc_setup文件,将以单独命令行形式完成整个DC过程。

module full_adder(

input clk ,

input rstn ,

input [31:0] a_in ,

input [31:0] b_in ,

input [0 :0] c_in ,

output reg [31:0] sum_out ,

output reg [0 :0] c_out

);

wire c_out_w ;

wire [31:0] sum_out_w ;

assign {c_out_w,sum_out_w} = a_in + b_in + c_in ;

always @ (posedge clk) begin

if(!rstn)

c_out <= 1'b0 ;

else

c_out <= c_out_w ;

end

always @ (posedge clk) begin

if(!rstn)

sum_out <= 32'h0 ;

else

sum_out <= sum_out_w ;

end

endmodule

准备完毕后在work目录下输入命令dc_shell启动DC。

设置搜索路径,搜索路径设置为work目录下的library目录。命令set_app_var search_path ./library/。

设置target_library和link_library,给二者设置相同的库。命令分别为set_app_var target_library slow.db、set_app_var link_library slow.db。

工艺库设置完之后,读入设计文件,命令为read_file -format verilog {../../rtl/full_adder.v},路径可以是相对路径,也可以是绝对路径。

导入完成后会显示如下信息,包含输出信号的类型和位宽。输入命令check design可以验证代码是否读入成功,返回1代表没有错误。

文件导入完成后进行设计约束了,首先对时钟进行约束,创建周期为10ns的主时钟,命令create_clock -period 10 [get_ports clk]。

给输入引脚设置相关的输入延时,给除了时钟以外的所有输入引脚都设置input_delay为1,并且输入的input_delay是相对于clk而言的,命令set_input_delay -max 3 -clock clk [remove_from_collection [all_inputs] clk]。DC显示1,表示设置完毕。

设置输出端口的output_delay,设置输出的最大output_delay为2.5。命令set_output_delay -max 2.5 -clock clk [all_outputs]。

设置所有输入信号的transition time,即信号翻转时间,设置为0.15,命令set_input_transition 0.15 [all_inputs]。约束设置完,再check_design一下确认没有问题,显示1表示没有问题。

约束设置完成后开始综合,命令compile。

综合时DC会输出一些报告,最后显示优化完成。

综合完成后,可以查看一些报告,比如可以输入命令report_clock查看时钟报告。

输入命令report_timing查看时序报告,看在我们设置的时序约束下,整个设计是否会出现时序违例。

如上图,时序裕量为正,slack显示MET,表示满足要求,如果时序违例,会显示VIOLATE。

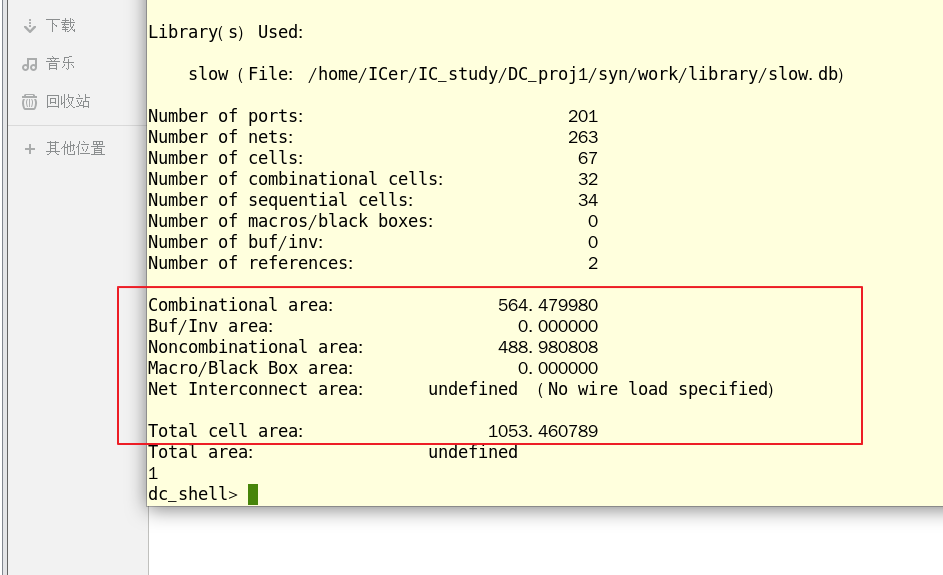

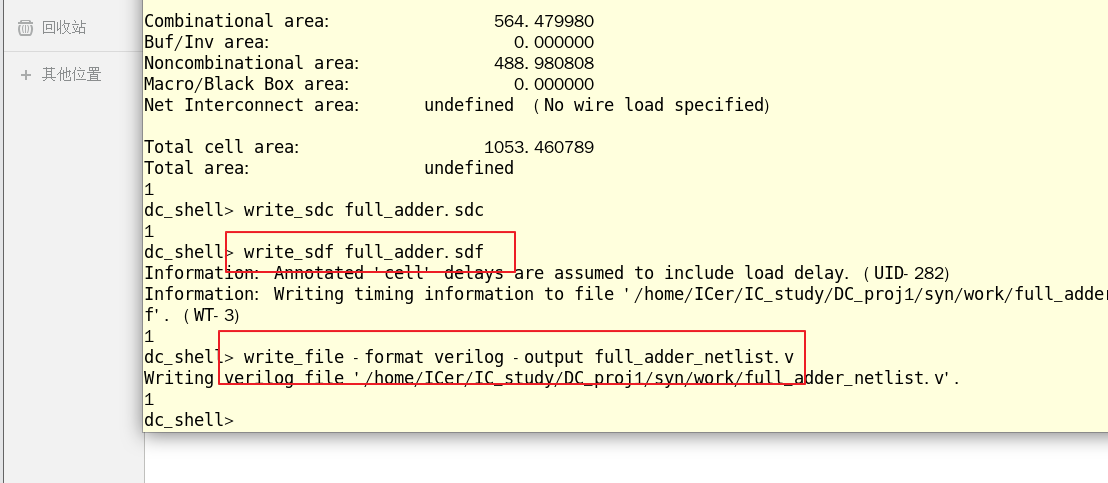

输入命令report_area查看综合后的面积报告。

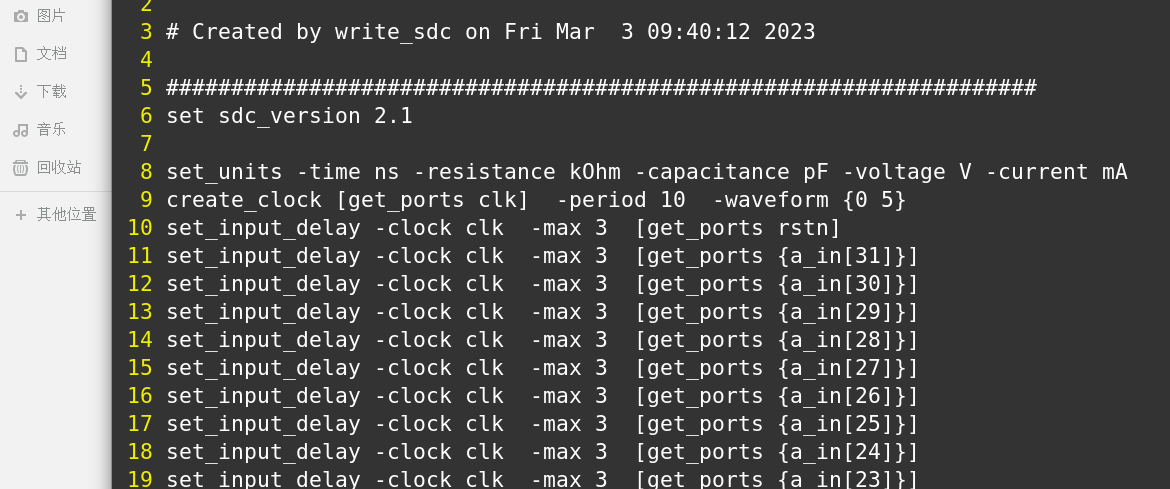

输入命令write_sdc full_adder.sdc保存约束信息,.sdc文件为时序约束文件。

.sdc文件如下图,内容就是之前命令设置的时序约束。

输入命令write_sdf full_adder.sdf保存用于做后仿的时延文件,跑后仿除了时延文件,还需要综合后的网表文件。

输入命令write_file -format verilog -output full_adder_netlist.v输出门级网表文件。

门级网表文件内容如下图,主要包含基于工艺库的门级电路。

综合的简单过程主要以上内容。

参考资料

[1].https://www.bilibili.com/read/cv17138007