接上篇跨时钟域设计(一)。

3. 跨时钟域处理

跨时钟域处理的目标是100%确保数据(事件)在跨时钟时的完整性,包括数据的值不能错,数据的顺序不能错和数据的个数不能错。

...

- 芯片设计

- 2023-03-27

1. 同步时钟/异步时钟

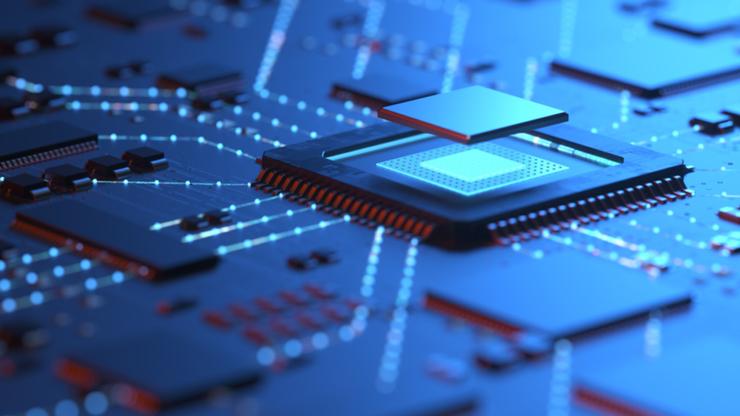

在目前芯片或IP设计中,只有一个时钟的可能性很小,通常有好几个时钟,比如接口上有一个时钟控制数据进出,Core如ARM也存在CPU时钟,DDR控制部分也存在较高频率的给DDR

...

- FPGA学习

- 2023-03-25

5. RTL Coding

当前面部分设计的比较详细后,开始RTL代码编写,我使用的整个EDA工具都是在Linux上完成的,RTL代码使用GVIM编写。

...

- 芯片设计

- 2023-03-24

按照前面数字IP设计流程。

1. 设计需求

设计1个bin2BCD简单IP,BCD编码为二进制表示的十进制编码。

...

- 芯片设计

- 2023-03-24

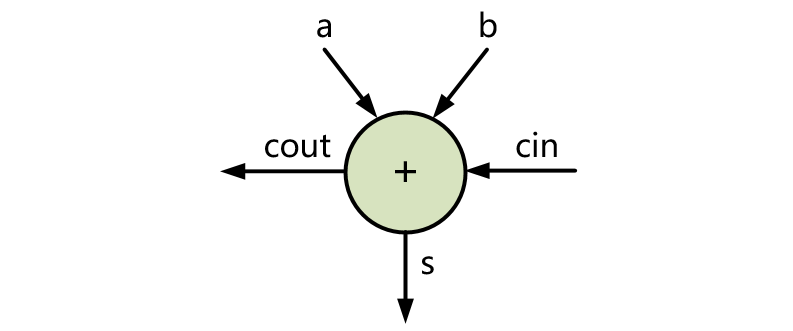

数字IP设计流程如下图所示,设计需求分析主要是分析要设计一个具有什么功能的IP,数据量有多大,要达到多少的频率等等。

设计需求分析完成后模块通常主要分为两种类型,一种是算法型,一种是接口协议类型。

...

- 芯片设计

- 2023-03-24

DC综合实践

首先为工程设计建立好文件夹,如下图,设计目录为DC_proj1,设计目录中包含doc、rtl、syn等目录,doc目录用于存放工程文档,rtl目录用于存放设计rtl文件,syn用于DC

...

- 芯片设计

- 2023-03-04

IC学习 | Design Compiler综合学习总结(一)

1 综合概述

综合是IC前端设计中的重要步骤之一,综合的过程是将行为级描述的电路、RTL级的电路转换到门级的过程。

...

- 芯片设计

- 2023-03-03

1.基本电路单元原理

1.1 组合逻辑

组合逻辑为输入信号电平变化,输出信号经过一个组合逻辑延时会马上发生变化。

...

- 芯片设计

- 2023-02-27

1.基础知识

硅(Si)是一种半导体,通常作为数字芯片的物理材料。由于它的所有价电子都参与了化学键,因此纯净硅是一种不良导体。但是它的导电性可以在硅中引入称为参杂剂的少量杂质来提高。

...

- 芯片设计

- 2023-02-24