1.基本电路单元原理

1.1 组合逻辑

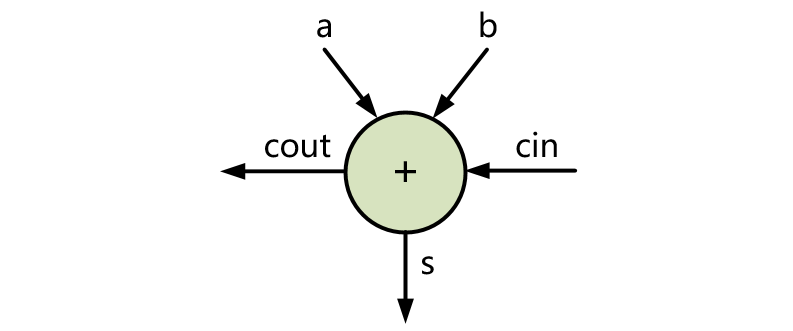

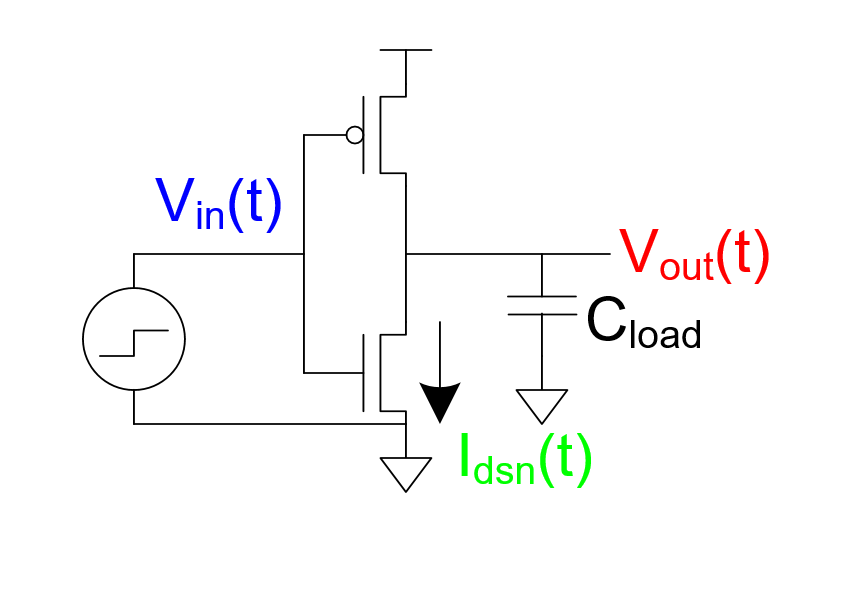

组合逻辑为输入信号电平变化,输出信号经过一个组合逻辑延时会马上发生变化。按照如下图的反相器电路模型,影响组合逻辑延时的因素主要有以下两点:

-

输入管脚(input pin)的transition time; -

输出管脚的电容大小。

输入管脚transition time越大,组合逻辑的延时越大,输出管脚的电容越大,延时也越大。

1.2 时序电路

时序逻辑电路与组合逻辑不同的是它具有存储功能,也就是说当输入发生变化时,输出可能会维持上一个状态不变。

1.2.1 锁存器(latch)

Latch的功能可以描述为:当EN为1时,D端的值输出到Q端,而当EN为0时,Q端保持EN为1时的Q端最后状态。

锁存器是时序电路中的基本构件元素。锁存器没有任何时钟信号,即为异步时序电路。

锁存器的延时可以分为EN到Q延时和D到Q延时。EN到Q延时:如下图,在EN为1之前D是稳定的1,但是当EN为1后,Q端没有马上变为D端的值,存在了一部分延时,这个延时即为EN到Q的延时。D到Q端延时:如下图,在EN为1之后稳定了一段时间,在这段时间内,D端电平发生了变化,理想状态应为EN为1,D端发生变化,Q端应该马上改变,但是实际并不会马上变化,而是等D端电平变化后延时一段时间后,Q端才输出D端的值,这个延时即为D到Q的延时。

1.2.2 触发器(Flip-Flop)

下图为D触发器,触发器的功能为在“CK”的上升沿把此时D端的输入值锁存到Q端输出,其他状态下D端的值不论怎么变化,Q端都不会发生变化,保持锁存的值。可以理解为眨眼睛,在上升沿时刻眨一次,看到D端的值,锁存输出到Q端,而其他情况下都是闭眼。“CK”为D Flip-Flop(DFF)的时钟输入。DFF也有下降沿触发的。

DFF的延时定义为CK到Q的延时,与锁存器(latch)的EN到Q延时类似。

为什么DFF只描述CK到Q延时,而没有D到Q延时?

这个问题需要掌握D触发器的建立时间(Setup)和保持时间(Hold)知识。

1.2.3 建立时间/保持时间

下图为DFF的CK和D的波形,A、B、C、D都为时钟的上升沿位置,可以看到,在A时刻,无法准确的确定D端的值是0还是1,B时刻也是一样,这样在A和B时刻,Q端也就无法准确的输出D端的值;而C和D时刻,由于在上升沿前面和后面,有一段D输入值的稳定时间,所以,在上升沿时刻,D端的值是确定的,因此,也就能输出准确的Q值。

所以为了使得DFF能正常工作,定义了建立时间(Setup)和保持时间(Hold)。建立时间是指在时钟上升沿到来之前数据必须保持稳定的时间,也就是在CK上升沿之前,D需要稳定的时间。建立时间是Setup requirement,也就是DFF能正常可靠工作的一个需求。

保持时间是指在时钟上升沿到来之后数据必须保持稳定的时间,也就是在CK上升沿之后,D需要继续保持稳定的时间。保持时间也是Hold requirement。

为什么DFF只描述CK到Q延时,而没有D到Q延时?

”

是因为触发器本身就有建立时间和保持时间的需求,只需要在上升沿满足建立时间和保持时间,那么上升沿时刻就能将信号锁存,因此只有一个CK到Q延时。

影响DFF setup/hold大小的因素有两个,可以通过代工厂提供的cell lib文件查看。

-

“CK”pin的transition time; -

“D”pin的transition time。

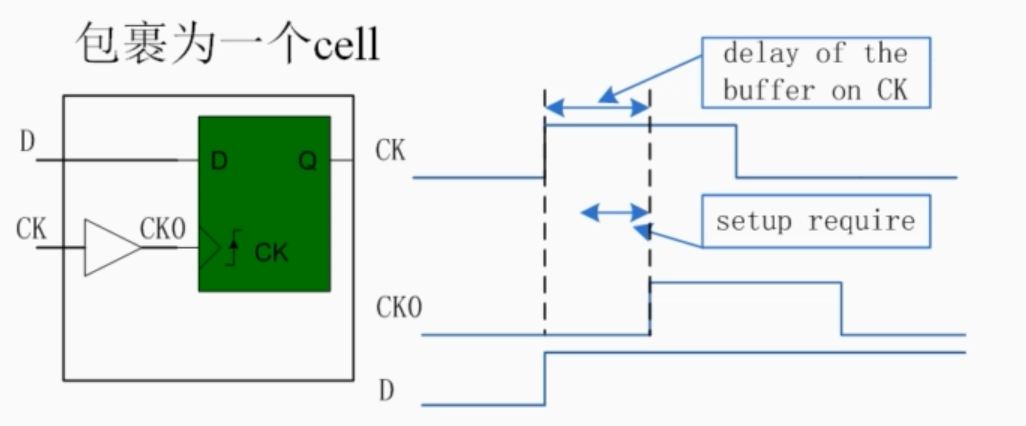

一个DFF Cell的setup requirement,在cell library里可以为0吗?

”

可以,可以做一个setup需求为0的DFF Cell。可以在CK前加一个buffer,如下图,CK和D是同时变化的,也就是在不加buffer情况下,setup为0,加上buffer后,在CK0的角度来看,CK0端采集信号满足了setup时间。将buffer和DFF包装成新的cell,则相对于外部,这个cell的setup时间为0。如果将buffer增大,甚至可以做成一个setup时间为负的cell。

一个DFF Cell的hold requirement,在cell library里可以为0吗?

”

也可以,与上面类似,只不过将buffer加到D端,再包装为一个新cell。

一个DFF Cell的setup requirement和hold requirement,在cell library里可以同时为0吗?

”

不可以。通过上面两个问题,在最底层的cell,仍然是存在setup/hold的,只不过是通过加buffer的方法,将这个窗口滑动了一下,但是不能没有这个窗口。

Setup+hold定义了一个时间窗口,在这个时间窗口内,“D”端输入信号不能发生变化,这样就保证了D端信号被采集并锁存到Q端。如下图,setup+hold时间都是0.3ns,但是setup和hold有正有负。

1.3 Cell驱动能力

一个Cell的驱动能力(driven strength)主要与构成这个Cell底层的MOS管有关,如果把MOS管的尺寸或面积做的更大,那么流过MOS管的电流更大,充放电速度也就越快,驱动能力就越强。

在cell library中,对同一个功能的cell,通常会给出不同驱动能力的几种cell。比如对同一个2输入与非门,会有nand2×1,nand2×2,nand2×4,nand2×8,nand2×16几种cell。

提供不同cell的原因是让芯片优化有更大的空间。芯片优化主要有几种方法(PPA),P为性能,P为功耗,A为面积,每一款芯片它实际侧重的方面可能不太一样,如有的会注重性能,而有的因为其他实际因素,可能会对性能做一些让步,注重考虑芯片功耗和体积。

参考资料

[1].https://www.mrchip.cn/newsDetail/573

[2].https://book.douban.com/subject/4322694/