1 综合概述

综合是IC前端设计中的重要步骤之一,综合的过程是将行为级描述的电路、RTL级的电路转换到门级的过程。数字IC综合一般使用的软件工具为Synopsys公司的Design Compiler,它可以将HDL等硬件描述语言描述的电路转换为基于工艺库的门级网表。

综合主要包括三个阶段:转换(translation)、优化(optimization)与映射(mapping)。综合工具首先将HDL等硬件描述语言描述的电路转换成一个与工艺独立(technology-independent)的门级网表,然后根据设计者添加的比如延时、面积等方面的约束条件,对门级网表进行优化,最后再根据具体指定的工艺库,将该门级网表映射到工艺库上,成为一个基于工艺库的门级网表。

下图表示了一个设计从最初的抽象概念的阶段到最终芯片阶段的转化过程。在这个过程中,Design Compiler主要完成将设计的RTL级描述转换到门级网表的过程,比RTL级更高的行为级的综合,将由Synopsys的另外一个工具——Behavior Compiler完成。因此,本文内容重点围绕RTL级综合为门级网表进行。

2 DC综合

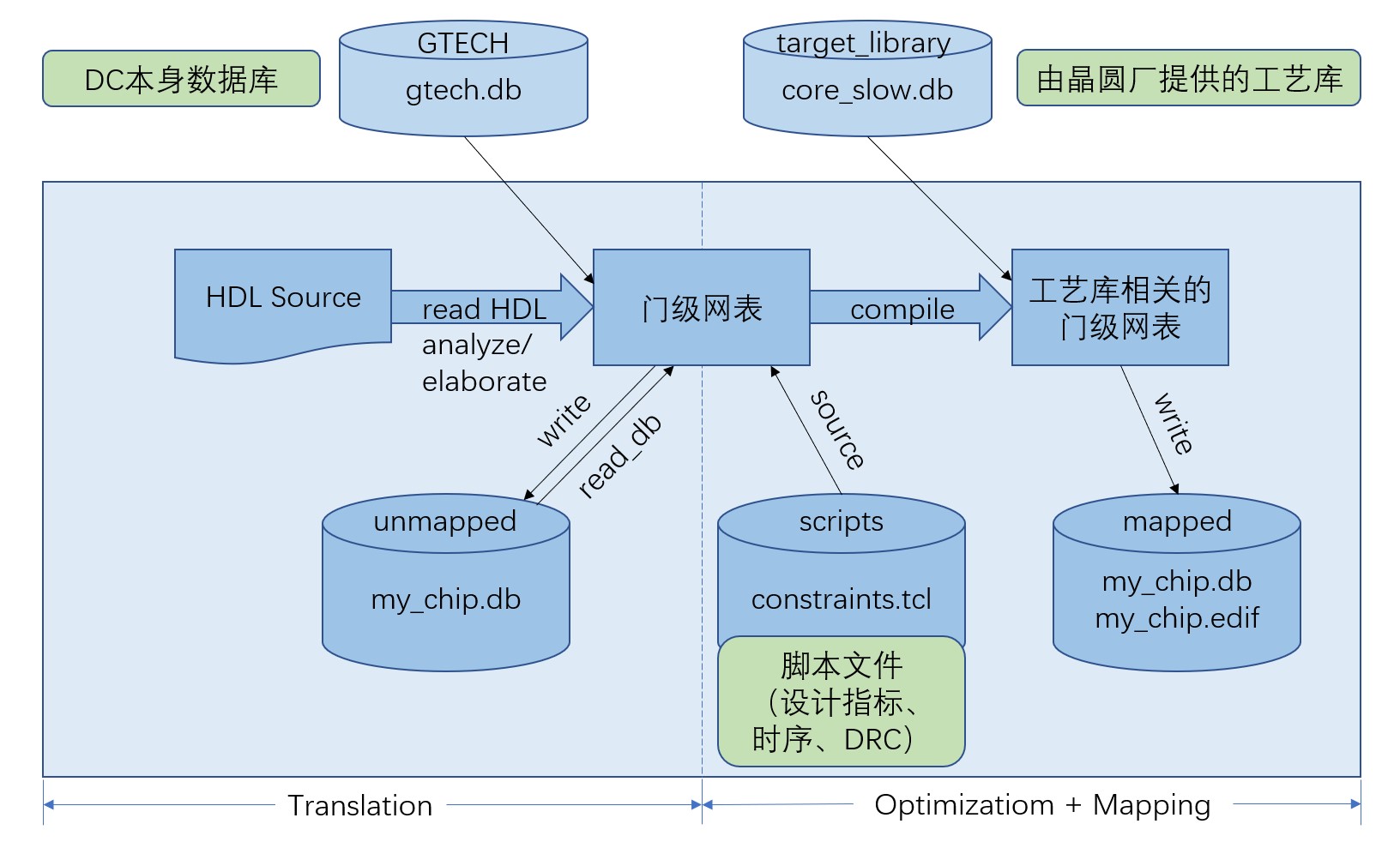

DC综合与一般综合过程相同,也包含转换、优化和映射三个阶段。如下图,转换阶段综合工具将HDL语言描述的RTL电路或未映射的电路用工艺独立的门级逻辑来实现,对于Synopsys的综合工具DC来说,就是使用gtech.db库中的门级单元来组成一个中间的网表,即在约束下转换成DC内部统一的门级描述的电路。优化与映射是综合工具对已有的中间网表进行分析,去掉其中的冗余单元,并对不满足约束条件(如constraints.tcl)的路径进行优化,然后将优化之后的电路映射到由制造商提供的工艺库上(如core_slow.db)。

DC综合在设计流程中的位置如下图所示。

2.1 Design Compiler启动

DC有三种启动方式,分别为GUI、dc_shell和batch mode。

-

GUI:

DC的图像化界面格式。大规模设计不可能用这种方式。启动命令为在终端输入design_vison,可以通过design_vision -help命令来查看DC的启动选项。

-

dc_shell:

DC以命令行的格式启动,启动命令在终端输入:de_shell。

-

Batch mode:

批处理模式,前面两种启动方式只是将DC启动,但是并没有综合工程,需要用命令进行配置后,DC才能开始综合。而批处理模式,在启动的同时,配置了DC该执行哪些脚本。

例如:dc_shell -topo -f run.tcl | tee -I run.log命令表示使用拓扑模式启动DC,同时执行run.tcl脚本,并且把启动过程信息记录到run.log中。

目前,DC启动主要使用dc_shell和批处理两种启动方式。

2.2 库文件

2.2.1 符号库(symbol_library)

符号库是定义了单元电路显示的Schematic的库,用户如果想启动DC GUI界面查看、分析电路时需要设置符号库。设置符号库后在使用GUI界面的时候,就可以看到综合后的门级网表的图形化界面。

TSMC 90nm库里的符号库如下图所示。

2.2.2 综合库(synthetic_library)

综合库一般为Synopsys的库:DesignWare library和标准单元库。DesignWare library是Synopsys的IP库,当使用Synopsys公司的IP核的时候比如使用了乘法器IP,那么就要添加DesignWare library到综合库中。同时需要在link_library中设置相应的库以使得在链接的时候DC可以搜索到相应运算符的实现。

DesignWare library和标准单元库在DC软件路径如下图所示。

2.2.3 目标工艺库(target_library)

目标工艺库是DC将RTL级的HDL描述最终映射到实际的门级电路所需要的标准单元库。读入的HDL代码首先由Synopsys DC工具自带的GTECH库转换成DC内部的RTL级网表,然后映射到工艺库和优化生成门级网表。

目标工艺库由Foundary提供,格式一般为.db格式,这种格式是DC认识的一种内部文件格式,不能由文本方式打开,想查看目标工艺库可以找到和.db格式同名的.lib格式文件,它们包含的信息一样,.db无法文本查看,而.lib可以文本查看。

TSMC 90nm库里的目标工艺库如下图所示。

2.2.4 链接库(link_library)

链接库设置模块或单元电路的引用,对于所有DC可能用到的库,都需要在link_library中指定,其中也要包括用到的IP库。

IP核可能是已经综合到门级的网表文件,当作设计文件读入时,就需要把link_library设置成指向生成该门级网表的库,否则DC因为不知道该门级网表中门单元电路的功能而报错。

在设置链接库路径时,最好在路径前加*号,表示DC在引用实例化模块或单元电路时首先搜索已经调进DC memory的模块和单元电路。如果不加*号,DC就不会使用DC memory中已有的模块,可能会出现无法匹配的模块或单元电路的警告信息。

加*号后会开辟一块单独的内存空间给DC使用,然后先搜寻内存中已有的库,然后再搜寻link_library指定的其他库。比如之前读入了库a,库a存在内存中,DC在综合的时候,引用实例化模块或单元电路时,缺少的东西会先在库a里找,找不到后再去设置的link_library路径中找。

一般情况下,只用一个工艺库,链接库需要引用目标工艺库,指定target_library;此外,如果用到IP核,需要指定其工艺库。

2.2.5 工艺库(technology_library)

链接库(link_library)和目标库(target_library)这两个库合称为工艺库。

TSMC 90nm工艺库路径以及库文件如下图所示。

2.2.6 搜索路径(search_path)

可以设置库的搜索路径,表示DC读取工艺库的路径,假如当读入一些工艺库时,忘了设置其库的路径,那么DC会根据这个路径去寻找库。

库的指定只需要指定target_libray和link_library,其他的可以不指定。

2.3 启动文件.synopsys_dc.setup

启动文件.synopsys_dc.setup就是在DC启动时最先读入的文件,DC启动的时候,会在如下的三个目录里自动搜索该文件,对DC的工作环境进行初始化。

-

DC安装位置的admin/setup目录下,包含了DC标准的初始化文件。一般不要动。

-

$home目录下,一般会包含用户本人使用的变量以及个性化设置。一般也不要动。

-

工程设计目录,一般会为设计建立目录以存放设计相关文件。可以自己建立setup文件并且修改。

上述三个目录中,后面目录里的setup文件会覆盖前面文件中的设置。该文件内容主要包含了库的设置、工作路径设置以及一些常用命令别名的设置等。

Setup文件主要定义下面这些内容:

-

SYN_ROOT_PATH:

设计目录路径,即工程总的设计路径,在这个路径下进行仿真、综合、形式验证等等。

-

RTL_PATH:

RTL文件路径,放置RTL文件的路径。

-

CONFIG_PATH:

配置文件路径,放置DC的一些配置文件,若无配置文件,可不进行设置。

-

SCRIPT_PATH:

脚本路径,放置约束脚本的路径。

-

UNMAPPED_PATH:

未映射文件路径,放置DC没有用工艺库进行映射时得到的文件,或者以ddc格式保存的未映射的文件。

-

MAPPED_PATH:

映射后文件路径,放置DC最终综合后得到的结果。

-

REPORT_PATH:

报告路径,放置DC运行过程中的一些报告,比如时序报告、面积报告等,通过产看这些报告,分析DC的综合结果是否满足要求。

-

WORK_PATH:

DC运行时路径。

-

DC_PATH:

DC安装路径。

2.4 读入设计文件

Design Compiler支持多种硬件描述的格式,如.db、.v、.vhd等等。文件读入就是将设计文件载入内存,并将其转换为DC的中间格式,即GTECH格式。

读入设计有两种实现方法:read和analyze & elaborate。二者区别为analyze & elaborate可以自由指定设计库,并生成GTECH中间文件前生成.syn文件存储于work目录下,便于下次elaborate节省时间,一般选择analyze & elaborate方法读入设计文件。

3 综合流程

使用DC进行基本的逻辑综合流程图如下。

3.1 准备设计文件

设计文件一般由verilog或VHDL等硬件描述语言编写,准备设计文件时,还需要考虑设计文件管理、设计分区和代码风格。

3.2 指定库文件

指定目标、链接、综合、符号等库。

3.3 读入设计

读取RTL级设计和门级网表。

3.4 定义设计环境

定义综合时环境,包括制程(process)、温度(temperature)和电压(voltage)等操作条件,负载(load),驱动(drive),扇出(fanout)等等,它直接影响设计综合和优化效果。

3.5 设置设计约束

可以使用上图中所示命令定义约束,包括时钟、延时、面积等。

3.6 选择编译策略

如果设计是分层的,可以选择自上而下或自下而上的策略,取决于特定的设计和设计目标。

3.7 编译

进行综合过程。

3.8 分析及解决设计中存在的问题

查看综合后综合报告,包括时序、面积、时钟报告。对报告分析是否满足设计要求。

3.9 存储设计数据

保存综合过程中的设计属性和约束,如门级网表文件、时序约束文件等等。

参考资料

[1].https://www.bilibili.com/read/cv17138007

[2].https://zhuanlan.zhihu.com/p/452563769

[3].https://www.cnblogs.com/IClearner/p/6621967.html

[4].https://www.cnblogs.com/IClearner/p/6617207.html

[5].https://zhuanlan.zhihu.com/p/129059203

[6].https://zhuanlan.zhihu.com/p/449527466

[7].Design Compiler User Guide Version P-2019.03, March 2019