接上篇跨时钟域设计(一)。

3. 跨时钟域处理

跨时钟域处理的目标是100%确保数据(事件)在跨时钟时的完整性,包括数据的值不能错,数据的顺序不能错和数据的个数不能错。

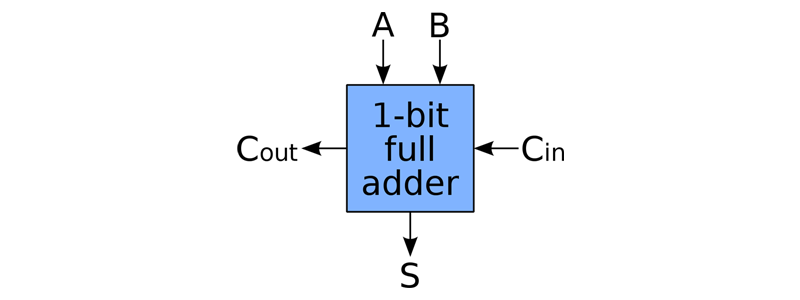

3.1 单bit跨时钟处理

单bit跨时钟域同步常用方法为将需要同步的单bit信号寄存器打两拍。

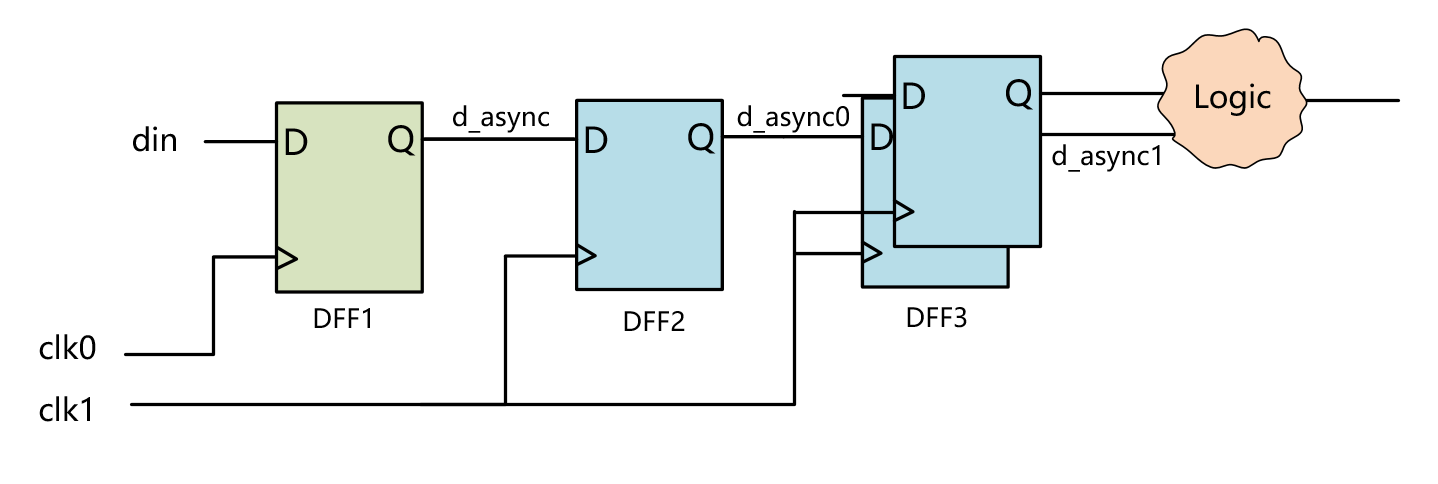

单bit跨时钟域同步处理电路如下图所示。

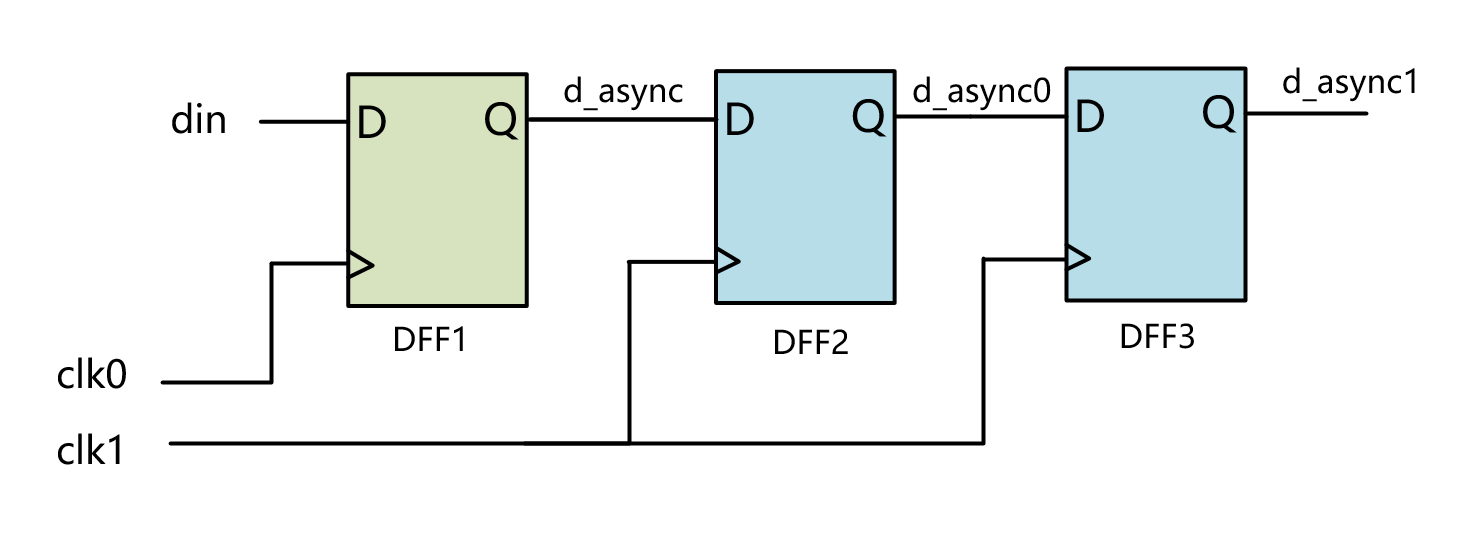

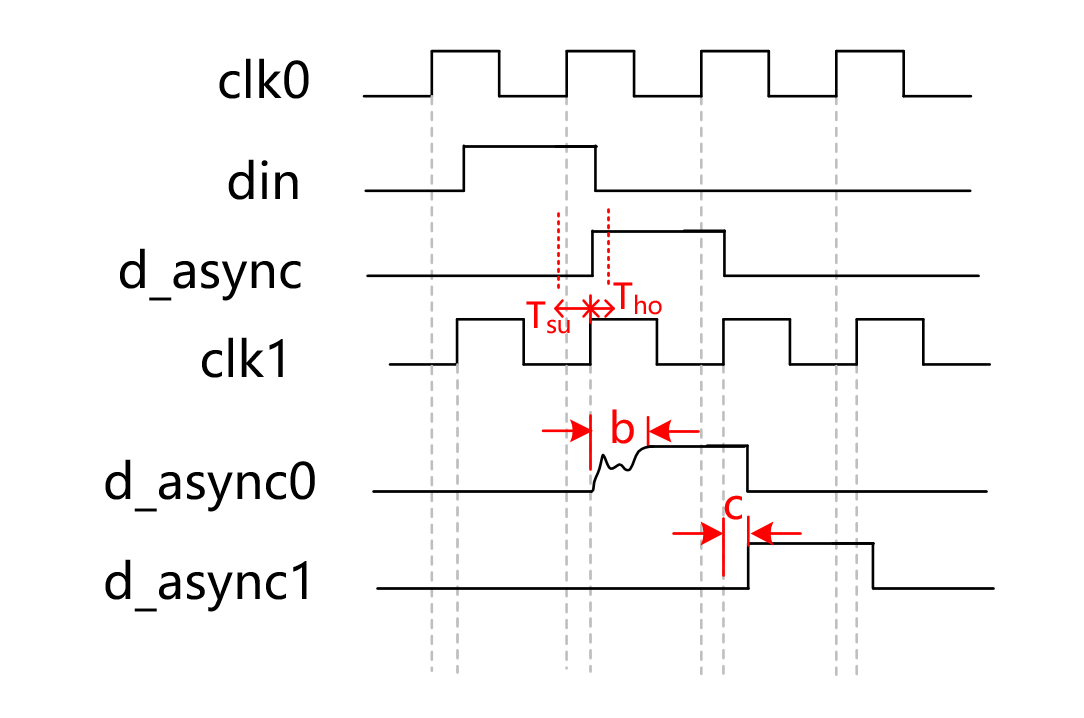

假设din波形如下图,DFF1在clk0时钟上升沿看到din后,经过正常CK-Q延时(图中a段),将D端数据锁存到Q端,但是d_async上升沿时刻刚好是clk1时钟的上升沿,这时候由于d_async不满足DFF2的Setup时间需求,DFF2会产生亚稳态,由于亚稳态会使得CK到Q时间延长,所以经过图中b段时间后DFF2的Q端(d_async0)将d_async端值锁存。

而在clk1的下一时钟上升沿,DFF3将D端d_async0值经过正常的CK到Q延时(图中c段)锁存到Q端d_async1。

因此,从上面分析中看到,要想d_async0保证能抓到d_async,就需要din/d_async保持一段时间,那din/d_async至少需要保持多久?

din/d_async至少应该保持的时间为:clk1时钟的一个周期+DFF2的Setup需求时间+ DFF2的Hold需求时间。原因如下:

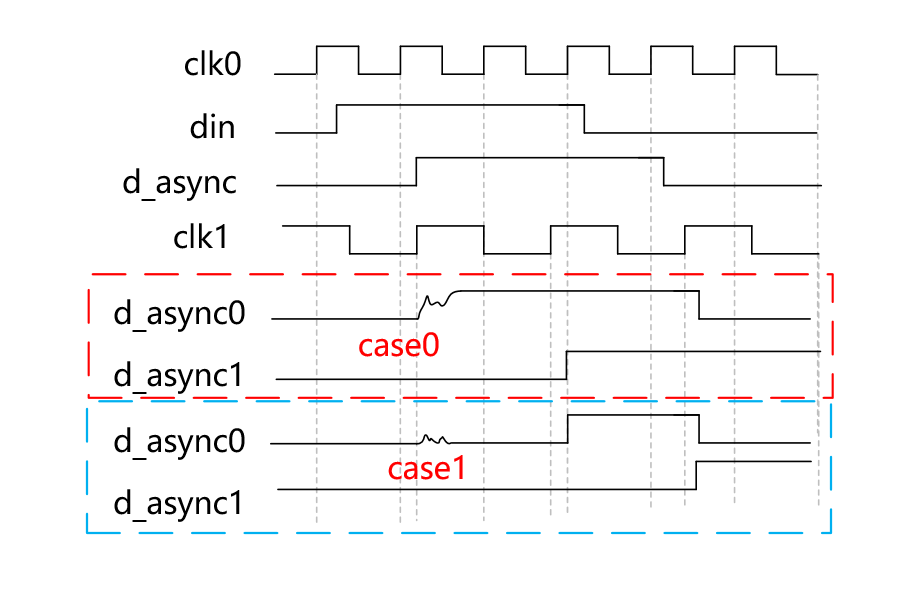

如下图,假设d_async的高电平刚好是clk1的一个周期,并且d_async的上升沿刚好是clk1的上升沿,那么d_async无法满足DFF2的Setup需求,可能DFF2在clk上升沿抓到的是d_async的高电平,那么经过亚稳态一段时间后d_async0为高电平,d_async1也能在下个clk1周期抓到d_async0的高电平值。

但是还有另外一种可能是,如下图,在a段由于不满足Setup需求,在c段由于不满足Hold需求,可能DFF2在a段clk上升沿抓到的是d_async的低电平,在c段clk上升沿抓到的也是d_async的低电平。这就会导致d_async1不会抓到有效的高电平信号,使得同步产生问题。

总之,如果din/d_async保持的时间不够,就会因为Setup/hold需求不满足原因而产生不确定情况。

单bit跨时钟域同步处理打两拍需要100%保证数据的准确性。100%保证有两个前提,第一是din信号要保持足够长的时间,才能保证被clk1时钟抓到;第二是DFF2亚稳态时,CK到Q的延时最大值,即最大的Metastable Time,这个最大的Metastable Time需要小于clk1时钟周期,这样就能保证DFF3不会发生亚稳态现象。

亚稳态出现后有两种情况,第一种就是DFF2在clk1上升沿看到的是d_async的高电平,那么d_async0/1波形如下图中case0;还有一种就是DFF2在clk1上升沿看到的是d_async的低电平,经过一段不确定状态的亚稳态时间后,最终d_async0输出低电平,如下图终case1,在下个clk1时钟周期抓到高电平,而d_async1得再延时一个周期Q才能输出。两种情况相差一个时钟周期。

3.1.1 错误的单bit同步电路

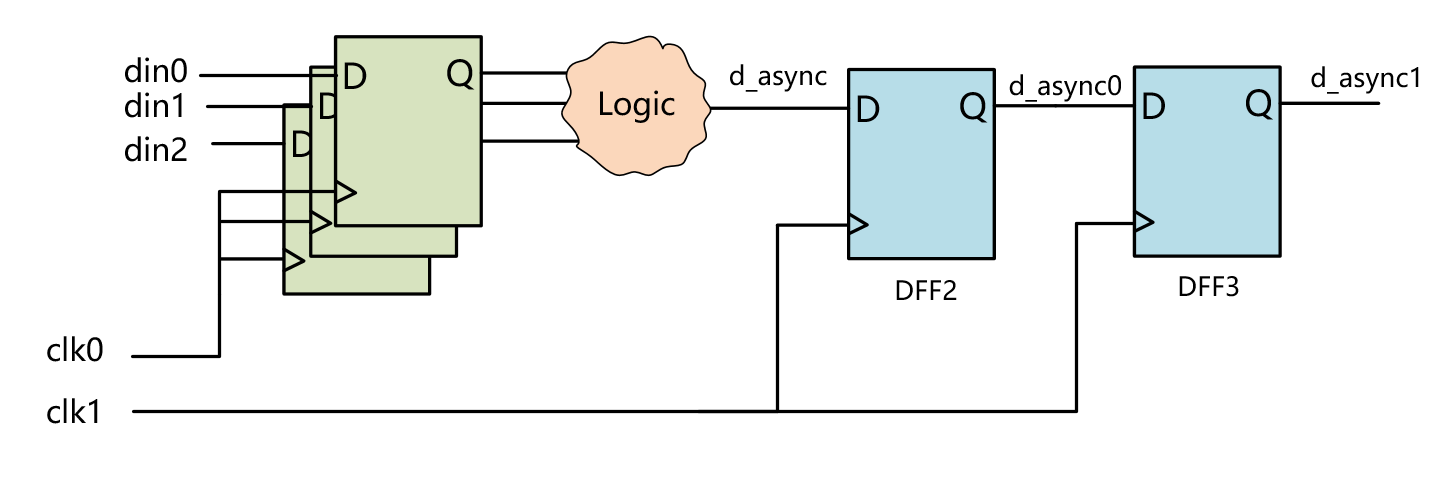

如下图的单bit同步电路是错误的。由于到达组合逻辑的路径延时可能不同,导致组合逻辑可能会出现Pulse。因为异步时钟的缘故,假如刚好这个不正确的Pulse被clk1时钟域的DFF2抓到,将会在DFF3中传递下去。

如下图所示的单bit同步电路也是错误的。因为可能会导致DFF3产生亚稳态。

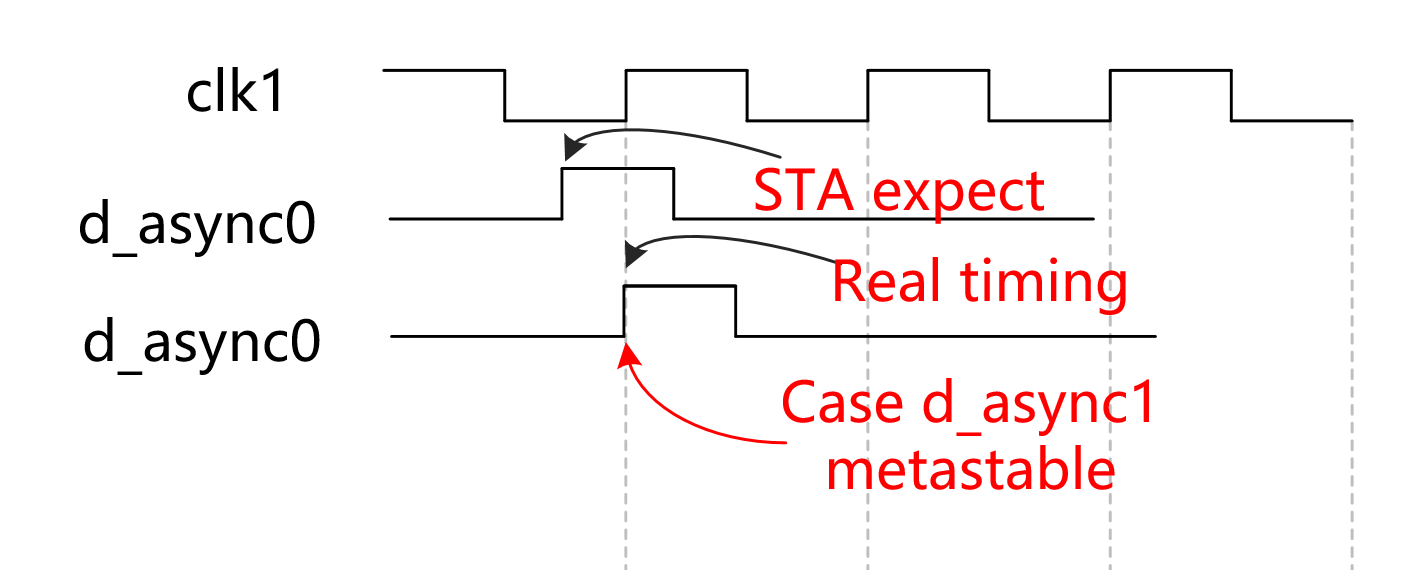

对时序工具来说,DFF2和DFF3是属于clk1时钟域的,异步下DFF2会亚稳态,时序工具它会按照正常的DFF的CK到Q延时去算DFF2经过组合逻辑到DFF3 D端路径的延时是否满足DFF3的Setup/Hold需求。但是,DFF2在亚稳态时它的CK到Q延时会比正常大很多,就可能会导致真实的d_sync0上升沿也在clk1的上升沿附近,可能会使DFF3也产生亚稳态。

3.1.2 正确的单bit同步电路

如下图,clk1时钟域的第二级寄存器过后就能放组合逻辑。因为在二级DFF后的信号可以保证数据同步的正确性。

3.2 多bit跨时钟处理

多bit跨时钟处理不能使用单bit跨时钟处理的并行方式,比如din[0]用单bit跨时钟域处理,din[1]也同时用单bit跨时钟域处理。这种方法处理多bit跨时钟同步是不对的。

多bit信号跨时钟域处理的方法有两种,第一种是使用握手信号对多bit数据进行异步握手;第二种方法就是使用异步FIFO。

需要注意的是,跨时钟域电路(CDC)无法通过RTL仿真去验证CDC电路的正确性,因为RTL仿真不会考虑DFF的CK到Q延时、DFF的Setup/Hold时间。

既然RTL仿真无法验证CDC的正确性,那么带Delay的gate level后仿能验证CDC的正确性吗?

”

答案是能验证,但是还不够。

首先带Delay的后仿,不管是时钟还是DFF,都是带了延时的,但是还不够是因为信号的翻转率或者仿真时间可能不够,因为异步电路,时钟之间没有关系,信号的延时也无法全部覆盖,不像同步电路模块RTL功能验证时能把功能点覆盖全。