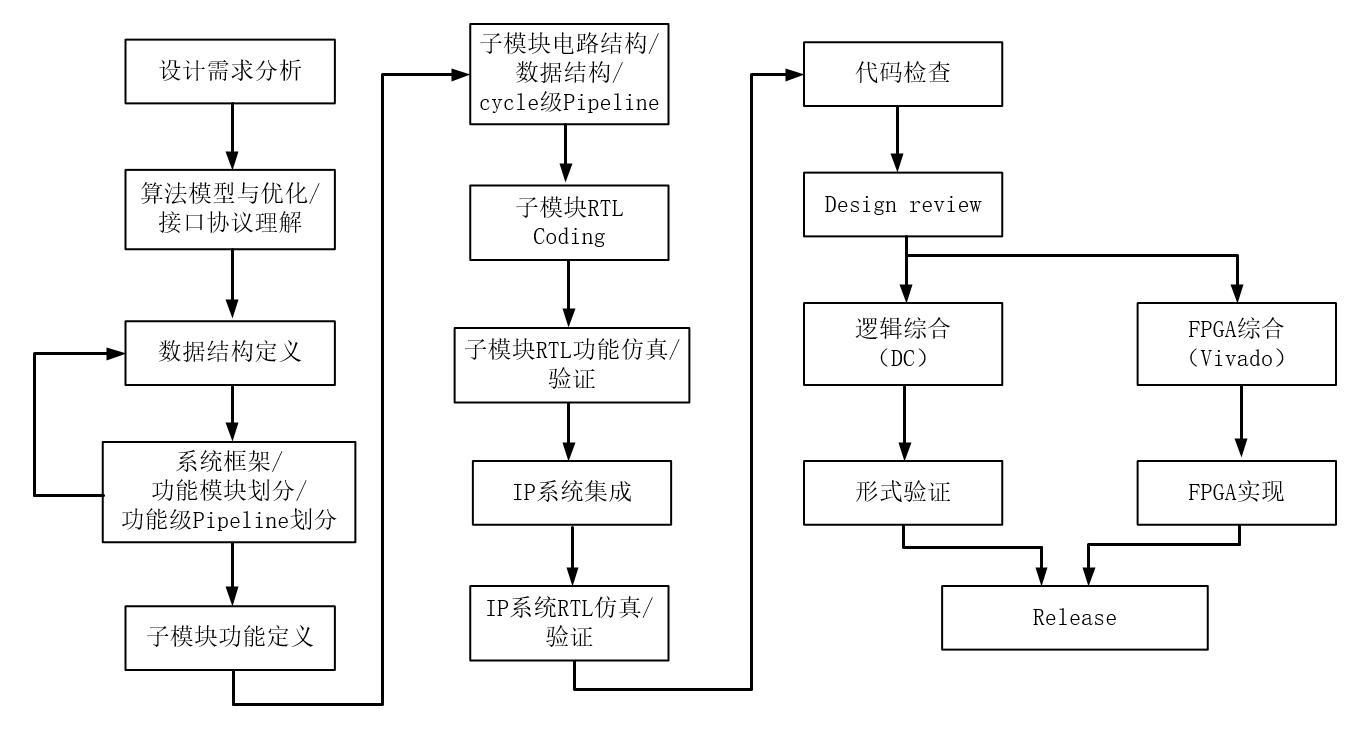

数字IP设计流程如下图所示,设计需求分析主要是分析要设计一个具有什么功能的IP,数据量有多大,要达到多少的频率等等。

设计需求分析完成后模块通常主要分为两种类型,一种是算法型,一种是接口协议类型。算法类型比如像CNN、图像滤波算法等等,需要将算法分解,有些具有复杂运算的算法更需要将复杂的运算如三角函数等等分解为加减乘等适合硬件去做的电路结构。接口协议类型比如像AXI、IIC、DDR3等协议控制,需要将整个协议理解。

接下来是数据结构定义和系统框架、功能模块的划分以及功能级Pipeline的划分,数据结构定义和系统框架主要就是要将做的IP的流程,包括数据通路、控制通路等设计清楚,将各个功能模块要完成什么样的功能都定义清楚,当涉及较大IP时,可能还有功能级的流水线划分。

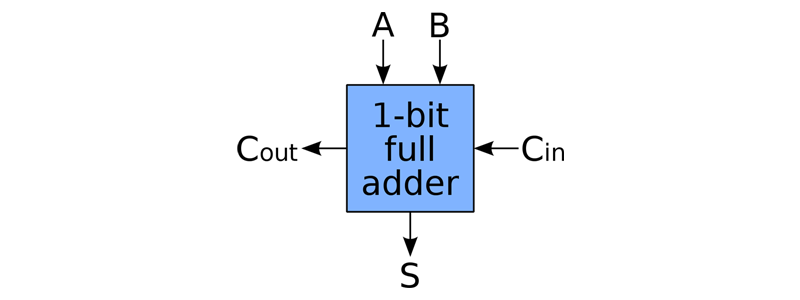

接下来就是子模块功能实现部分,包括详细的子模块功能、接口、时序等定义,还有子模块内部Cycle级的Pipeline划分等等。将这些定义的非常详细后进行RTL代码编写以及子模块功能的RTL仿真验证。

接下来就是将各个子模块集成、联立起来,进行IP顶层的RTL仿真验证,以及代码检查,看看是否由于代码风格问题,会有一些代码无法综合或者综合会产生问题等。

接下来对整个IP设计进行复盘,看看有没有地方还有能提升的地方。

然后就是综合,对于ASIC芯片来说,采用DC进行综合,综合后进行形式验证,形式验证主要就是害怕DC可能会有Bug,使得综合出来的门级与想要的功能有出入,因此,尽量悲观一些,通过形式验证再去检查是否功能正确,另一条路就是FPGA,在FPGA上可以较快的进行验证。

参考资料

[1].https://blog.csdn.net/qq_40677883/article/details/128997432