1.时钟意义

对于数字IC设计,系统时钟的重要性不言而喻。电路主要由两部分组成,一部分为组合逻辑电路,一部分为时序逻辑电路。组合逻辑电路无需时钟驱动,输入端电平发生变化,输出端结果随即发生变化(理想状态下,不考虑组合逻辑延迟时);而时序逻辑电路需要时钟驱动,因此,时序逻辑电路正常工作的前提是有稳定的时钟供给,并且在数字电路中,时序电路使用频率大大超过组合逻辑电路。所以,数字电路中,时钟资源以及时钟的布局,将对电路设计具有重要意义。

1.1 单时钟系统

对于简单的FPGA实验,系统设计中可能只有一个时钟域,系统下各模块共同使用这一个时钟。因此,单时钟域系统时钟树网络单一,时序分析难度较低。

1.2 多时钟系统

大部分项目工程设计包含较多功能模块,使用一个时钟想满足较复杂的系统设计肯定无法实现,因此,需要多个时钟为各个不同的模块提供时钟,自然而然,时钟网络就复杂起来,跨时钟域的时序分析难度也将提升。对于多时钟域的系统,必须要搞清晰整个系统的时钟有哪些,为哪些模块提供时钟,时钟怎么去约束等工作,也就是要设计时钟树。

2.FPGA时钟资源

2.1 引言

本文以Xilinx 7系列FPGA为例,Xilinx 7系列时钟资源有着详细的官方文档(UG472),7系列FPGA时钟资源通过专用的全局时钟资源和区域时钟资源管理符合复杂和简单的时钟要求。时钟管理块(CMT)提供时钟频率合成、减少偏斜和抖动过滤等功能。

2.2 时钟资源及布局

2.2.1 时钟资源整体架构

在掌握Xilinx 7系列时钟资源及布局之前,需要先对FPGA芯片整体结构有一些了解。本文以Xilinx官方的VC709板卡(搭载了Virtex-7 690T-1761-2 FPGA)为例,在Vivado通过综合、布局布线操作后,打开Open Implemented Design后可以看到Device界面。如下图所示。

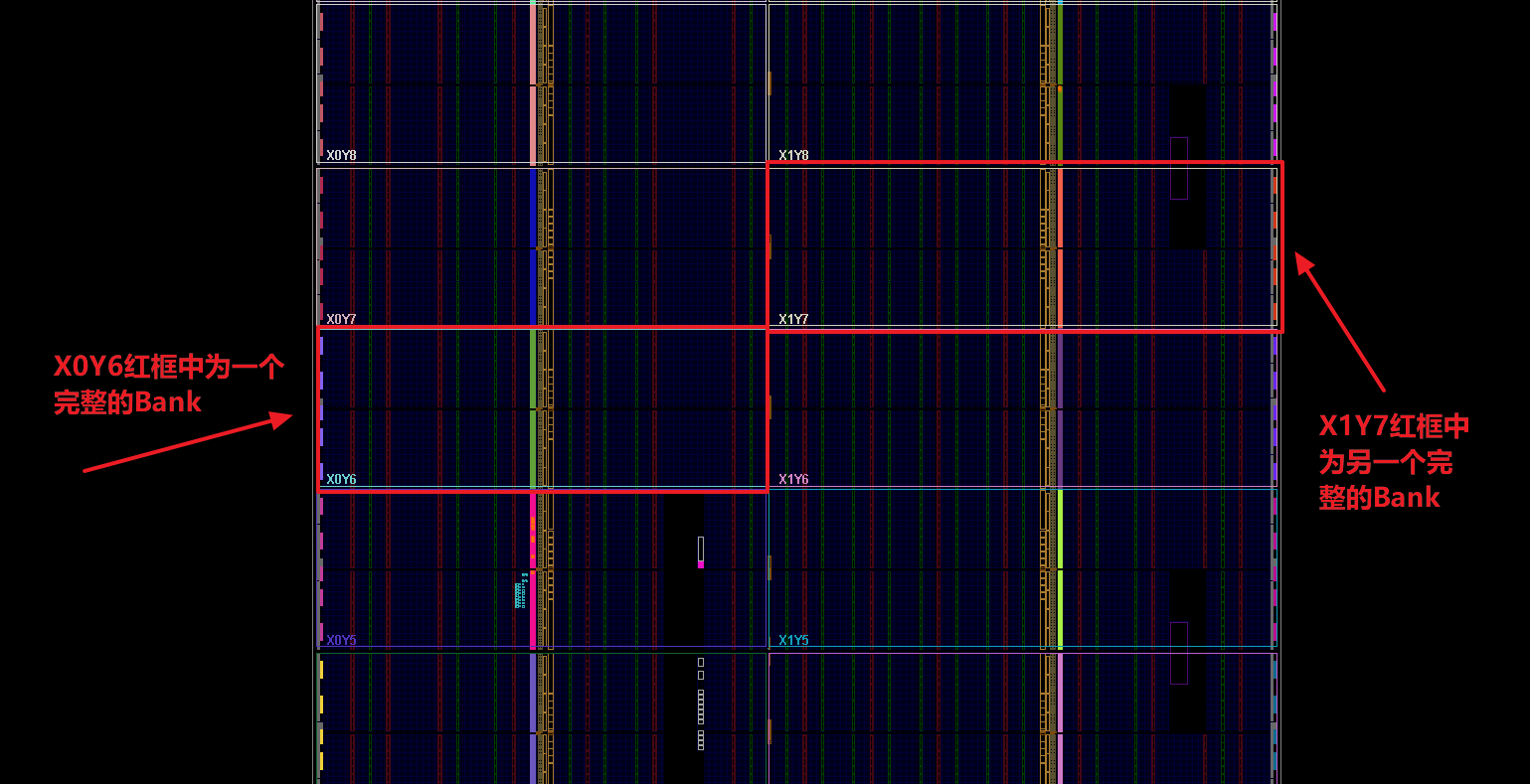

了解FPGA时钟资源布局,必须要了解Bank,下图红框中即为一个完整的Bank,一个Bank可以看成一个时钟区域。不同芯片时钟区域数量也不一样,从最小器件的1个时钟区域到最大器件中的24个时钟区域,小的、资源少的芯片时钟区域数较少,而大的,资源多的FPGA芯片时钟区域很多。

时钟区域详细划分如下图所示,垂直时钟中心线(Clocking Center 时钟主干线)将器件划分为相邻的左右区域,而水平中心线(Horizontal Center)将器件划分为顶部和底部。时钟主干中的资源被镜像到水平相邻区域的两侧,从而将某些时钟资源扩展到水平相邻区域。划分顶部和底部的水平中心线分割两组全局缓冲器(BUFGs),BUFGs不属于时钟区域,可以到达器件上任何时钟点。也就是BUFG在一定程度上分布在“Clock Backbone”中间,一般来讲,上半部分的16个BUFG时钟源来自上半部分的所有Bank,下半部分的16个BUFG时钟源来自下半部分的所有Bank,而BUFG的输出可以到达整个Device的任意位置。所有水平时钟资源包含在时钟区域水平时钟行(HROW)的中心,而垂直的、非区域的时钟资源包含在时钟主干或CMT主干中。

时钟区域包括50个CLB和1个I/O bank(50个I/O)的区域中的所有同步模块(例如:CLB、I/O、串行收发器、DSP、块RAM、CMT),其区域中心有一水平时钟行(HROW),每个时钟区域从HROW向上和向下跨越25个CLB(注意是跨越,并不是一个时钟区域中只有25个CLB,是从一列的角度来说HROW向上向下跨越了25个CLB),并水平跨域器件的每一侧。如下图所示。

HROW即水平时钟线,也就是BUFH或BUFG所走的线,下图可看到,每个Bank中间被BUFH分割开,时钟要想到Bank内的某个区域,则沿着水平时钟线想两侧延伸为其他器件提供时钟。

2.2.2 时钟区域内部架构

时钟区域中可用时钟资源及其基本连通如下图所示。

-

全局时钟缓冲器(BUFG)可以通过HROW进入每个区域,即使物理位置不在那里。 -

水平时钟缓冲器(BUFH)驱动通过HROW到达该区域的每个时钟点。 -

BUFG和BUFH共享HROW。 -

I/O缓冲器(BUFIO)和区域时钟缓冲器(BUFR)是位于I/O Bank内。 -

BUFIO资源仅驱动I/O时钟资源,而BUFR驱动I/O资源和逻辑资源。 -

BUFMR支持多区域链接BUFIO和BUFR。时钟功能的输入(CC)将外部时钟连接到时钟设备上的资源。

BUFH可以驱动同一Bank中的所有资源,BUFH位于Bank的一侧垂直居中,中间的分割线是有12条水平时钟线(HROW),与12个BUFH相连。BUFG也是通过连接到BUFH进而通过这12条水平时钟线驱动整个Bank的逻辑资源。每个Bank资源按照一定的规律进行排列,也就是每列有50个CLB、50个I/O引脚、10个BRAM,它们均匀的分布在水平时钟线(HROW)两侧。不同型号芯片每个Bank的资源是不一样的,但是每列的资源确实是固定的,只不过资源多的芯片每个Bank中的行数会增多。

2.2.3 时钟术语解读

7系列时钟架构,有很多术语,比如BUFG、BUFH、CC等等,下图为一个完整的Bank中常见的资源,当然,像CLB、BRAM、DSP不是时钟资源,但是标注一下可以有个大体的位置认识,下面对这些术语一一描述。

2.2.3.1 BUFG

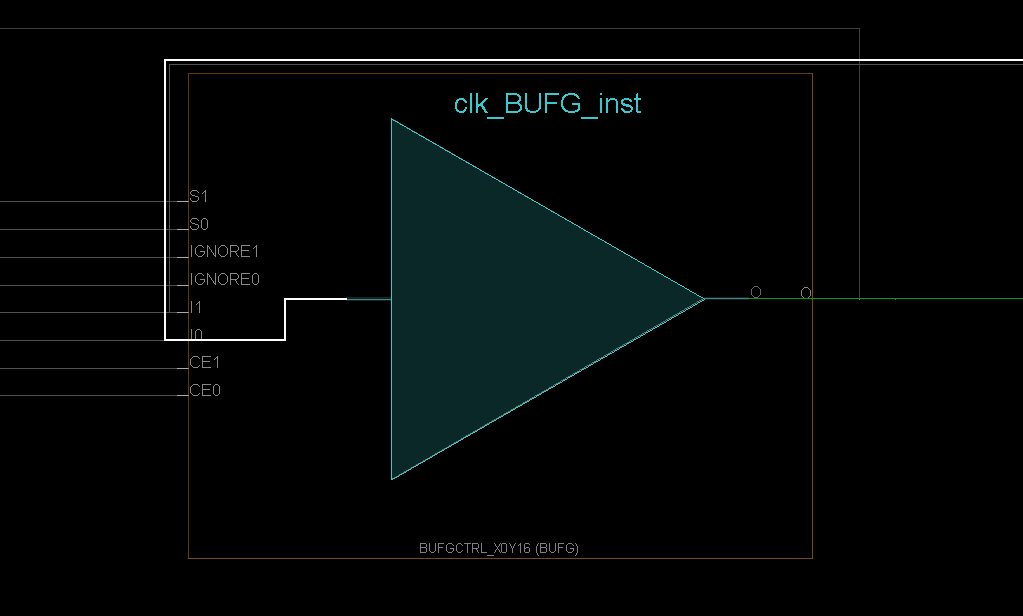

BUFG即全局时钟缓冲器,它的输入是IBUFG的输出,BUFG的输出到达FPGA内部的IOB、CLB、BRAM的时钟延迟和抖动最小。输入为固定管脚,输出为H型全铜全局高速网络,这样抖动和道道任意触发器的延时差最小。

IBUFG即输入全局缓冲,是与专用全局时钟输入管脚相连的首级全局缓冲。所有全局时钟管脚输入的信号必须经过IBUFG单元,否则会在布局布线时报错。

IBUFG后面连接BUFG的方法是最基本的全局时钟资源使用方法。如果全局输入时钟为差分时钟,则全局时钟输入管脚与IBUFDS连接,其作用与IBUFG相同,IBUFDS与BUFG相连,从而使用全局时钟。

下图为BUFG。全局时钟输入为差分时钟,经过IBUFDS后连接到BUFG,经过BUFG输出后供FPGA使用。

2.2.3.2 BUFH

BUFH即为水平时钟缓冲器,相当于一个功能受限的BUFG,其输出时钟只能通过HROW在左右相邻的时钟区域内工作。

2.2.3.3 BUFIO、BUFR、BUFMR

BUFIO即为IO时钟缓冲器,其输出时钟只能作用在一个时钟区域的IO寄存器处,无法在FPGA内部逻辑使用。BUFIO、BUFR都位于I/O Bank,所以它们是与引脚相关的区域时钟缓冲器,可有助于实现时钟源的同步采集等等。每个有引脚的Bank都有4个BUFIO和4个BUFR,2个BUFMRCE。

BUFIO它的作用是用来驱动I/O Bank里面的ILOGIC和OLOGIC。BUFR即为区域时钟缓冲器,其输出只能作用在一个市中区域里。与BUFIO不同的是BUFR可以驱动同一时钟区域的任何时钟点,可以看作是BUFH的mini版本。下图为BUFIO和BUFR的区别,可以看到,BUFR可以驱动同一时钟区域内部的其他逻辑资源,而BUFIO只能驱动IO。

BUFMR是多区域时钟缓冲器,之所以只有2个是对应MRCC,MRCC只有2个,它的作用是扩展时钟区域,输出既可以作用在本时钟区域,还可以通过CMT Backbone作用在上下相邻的两个时钟区域。即将某个Bank的时钟引入到上下相邻的Bank中去。如下图所示。

2.2.3.4 CC

CC即为外部时钟输入管脚,为“Clock-Capable“即时钟功能的缩写,表示具有时钟功能的引脚。并不是所有引脚都可以接时钟,有且只有通过特定的引脚才能将外部的时钟信号引入FPGA内部时钟资源。这个引脚有两种,分别称为MRCC(Multi-region clock-capable I/O)和SRCC(Single-region clock-capable I/O),Multi-region译为多区域,Single-region为单区域,而直观区别为MRCC可以连接到BUFMR上,但SRCC不可以,BUFMR具有时钟扩展功能。

CC在FPGA内部可以连接到BUFG、BUFH、BUFIO、BUFR、MMCM、PLL等,细致的CC管脚连接如下图所示。

每个Bank有50个IO引脚,其中有4对CC引脚,2对SRCC,2对MRCC。SRCC作为区域时钟使用时,只能连接到本时钟区域的BUFR和BUFIO,而MRCC可以通过BUFMR作用在上下相邻的时钟区域。它们都为差分的,如果单端时钟接到“P“上,对应的”N“引脚则不可用。

2.2.3.5 CMT

CMT Backbone:对于相邻时钟区域的时钟布线,可以不使用珍贵的全局时钟网络,而使用每个时钟区域都包含的CMT Backbone通道。

CMT Column:每个时钟区域都包含1个CMT,1个CMT由1个MMCM和1个PLL组成。

每个7系列FPGA最多有24个CMT。其中MMCM和PLL用作频率合成器,用于非常宽的频率范围,用作外部或内部时钟的抖动滤波器,以及降低时钟偏移。MMCM、PLL的功能总结为3点:

-

频率综合。 -

去抖动。 -

去偏斜。

2.2.4 时钟资源驱动关系

具体的时钟资源的驱动关系如下表所示。

| 对象 | 驱动源 | 驱动对象 |

|---|---|---|

| MRCC | 外部时钟 | 位于相同时钟区域和器件相同左/右侧的MRCC可以驱动: l 4个BUFIOs l 4个BUFRs l 2个BUFMRs l 1个CMT l 上下相邻Bank的CMT 相同顶部和底部MRCCs可以驱动: l 16个BUFGs 同一水平相邻时钟区域内的MRCC可以驱动 l BUFHs |

| SRCC | 外部时钟 | 同MRCC,但不能驱动BUFMR |

| BUFIO | CC、MMCM的CLKOUT0-3、CLKFBOUT或同Bank及上下相邻Bank的BUFMRs | 可以驱动同Bank的ILOGIC或OLOGIC |

| BUFR | 同BUFIO | 可以驱动CMT、任何BUFG可驱动的资源以及16个BUFG |

| BUFMR | MRCC和GT输出时钟可驱动 | 可以驱动上下Bank的BUFIO或BUFR |

| BUFG | 同一侧的CC、CMT、GT时钟、BUFR和邻近的BUFG | 可以驱动CMT、GT时钟、同侧BUFG和其他任何可接时钟的资源 |

| BUFH | CC、CMT、BUFG和GT时钟可驱动 | 可以驱动CMT、GT和同一时钟区域的任何时钟点 |

参考资料

[1]https://qiange.blog.csdn.net/article/details/127571939

[2]https://blog.csdn.net/gslscyx/article/details/114602573

原创文章,作者:hushan,如若转载,请注明出处:《FPGA | Xilinx FPGA时钟资源架构学习总结(一)》https://www.hushan180.com/38.html